Program

| Yasuharu Nishi, General Chair of InSTA 2016, The University of Electro-Communications, Tokyo, Japan | |

| |

Axel Rennoch Axel Rennochscientist and project manager at the Fraunhofer FOKUS Competence Center SQC, Germany | |

| Title: Test System Architectures using Advanced Standardized Test Language

The development of test suites using standardized test languages like TTCN-3 and UTP starts with an analysis of the external interfaces towards the system under test (SUT). Large and complex SUTs often require a distributed test system architecture that have to consider the test objectives and the introduction of multiple parallel test system components. The decomposition of a test system needs to be discussed and decided at the very beginning of the test development process. This presentation introduces different approaches from industrial test suite development projects and provides experiences with abstract test system architecture issues (e.g. synchronization, logging and maintenance).

Biography: | |

| Presentation file | |

Automatic Generation of UTP Models from Requirements in Natural Language | |

Presentation file Presentation file | |

| InSTA Discussion about emerging technologies | |

Hironori Washizaki Hironori Washizakihead and associate professor at Global Software Engineering Laboratory, Waseda University, Japan | |

| Title: TESEM: A Tool for Verifying Security Design Pattern Applications

Because software developers are not necessarily security experts, identifying potential threats and vulnerabilities in the early stage of the development process is often insufficient. Even if these issues are addressed at an early stage, it does not guarantee that the final software product actually satisfies security requirements. To realize secure design and implementation, we propose extended security patterns, which include requirement- and design-level patterns as well as a new model testing and model-based code testing process. Our approach is implemented in a tool called TESEM, Test Driven Secure Modeling Tool, which supports pattern applications by creating a script to execute model testing automatically (ARES'13, IJSSE'14, ICST'15). Moreover we recently extended the tool to support testing of security design patterns implementation by preparing testcase templates (ARES'14). By using the tool, developers can specify threats and vulnerabilities in the target design and implementation according to security design patterns, verify whether the security patterns are properly applied, and assesses whether these vulnerabilities are resolved.

Biography: | |

| Presentation file | |

A Study on the effectiveness of Test-Categories based test analysis | |

Presentation file Presentation file | |

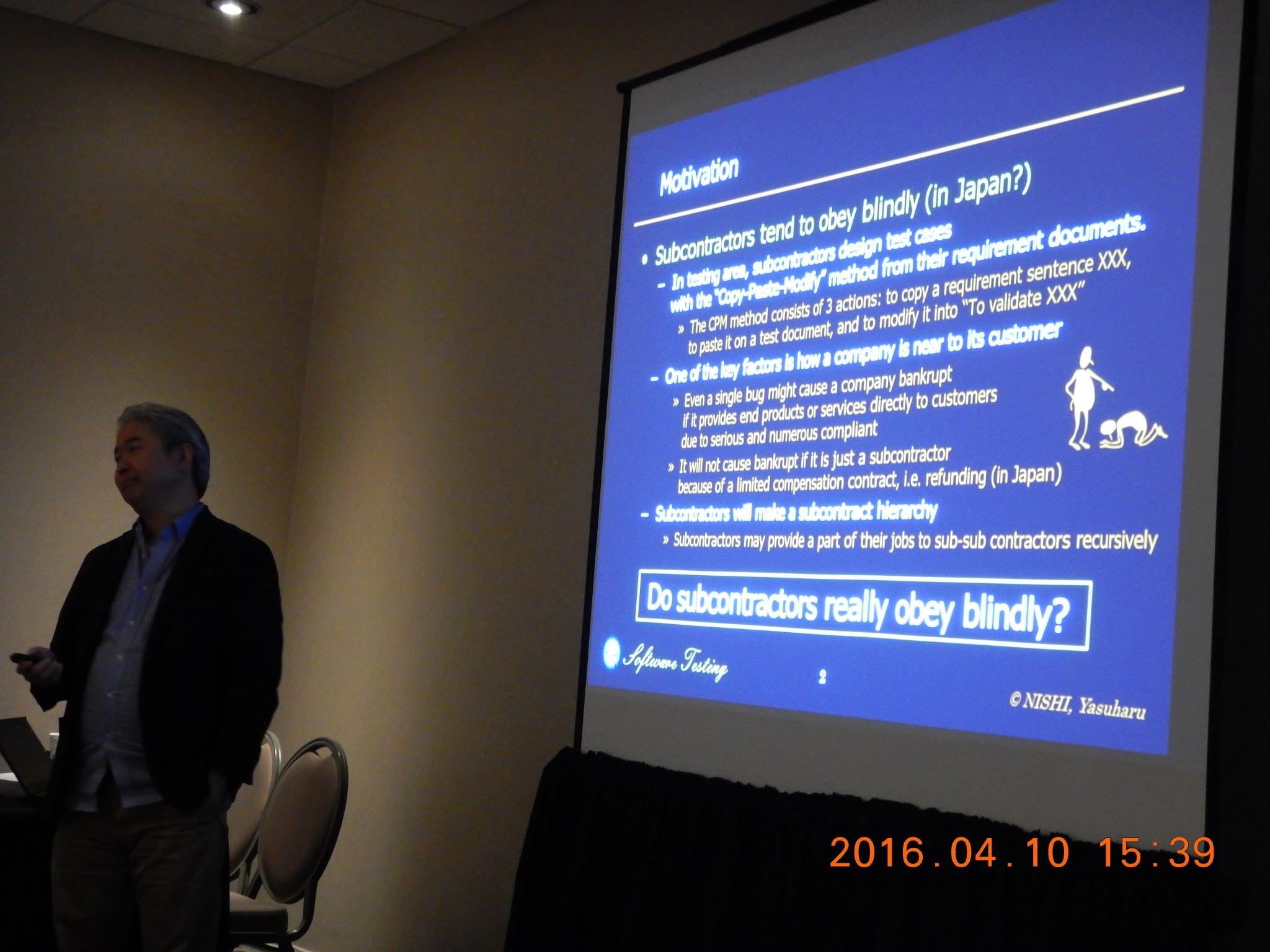

Difference in quality of test architecture between service providers and subcontractors | |

| |

| InSTA Discussion lead by Tsuyoshi Yumoto | |

| Yasuharu Nishi, The University of Electro-Communications, Tokyo, Japan |